6张图讲明白PCB Layout常见的那些坑

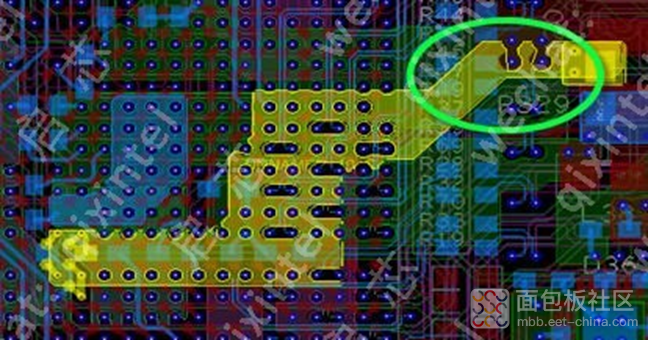

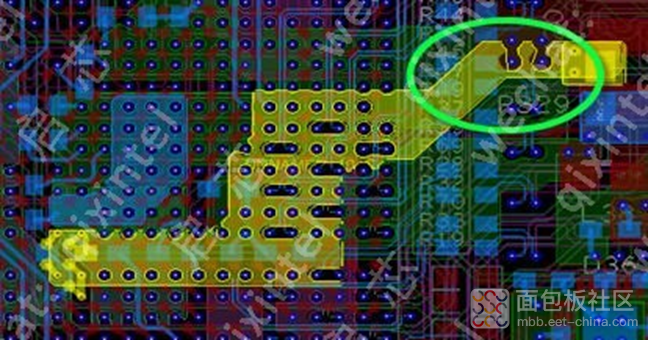

Review了大量的同事,以及客户的PCB设计,发现一个很常见的问题:很多时候,硬件工程师不注意就会打一排过孔,造成了把GND平面打断的现象。比如以下几张图中所示:上面这张图主要的问题是,被5个竖排过孔阻碍,有瓶颈。无法保证电流。 上面这张图,电源被过孔隔断,有瓶颈。需要加强。

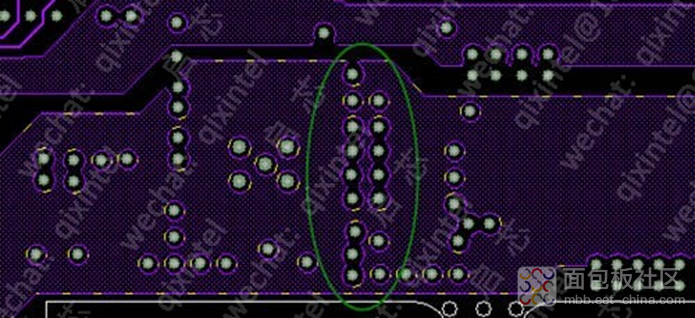

上面这张图,电源被过孔隔断,有瓶颈。需要加强。 上图的联排过孔,隔开了电源平面。电源铺铜有瓶颈,需要补强

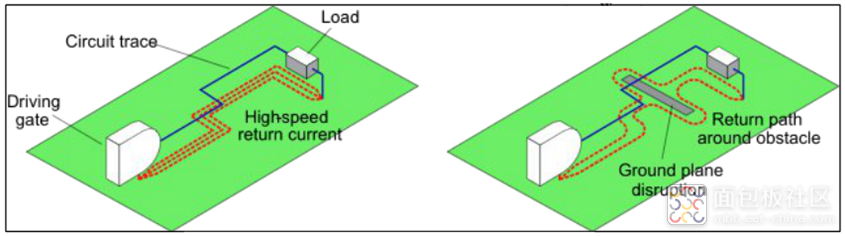

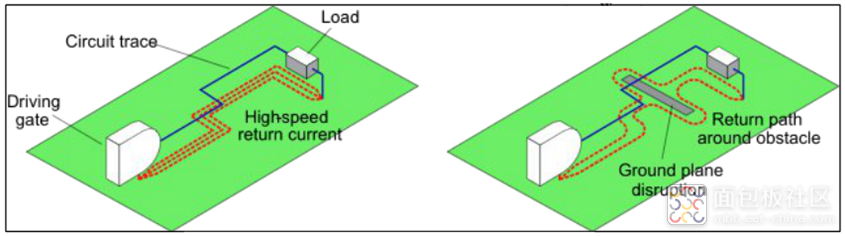

上图的联排过孔,隔开了电源平面。电源铺铜有瓶颈,需要补强 设计要求中有提到此网络有2A电流,目前一层铜皮由于过孔隔断无法满足载流要求,需要补强。这样的影响,首先是无法满足载流要求;其次,电流的回流路径加长,增加了噪声。减少PCB上高速信号的噪声辐射的一个基本原则是尽量减少电流回流路径的环路面积,高速信号的回流电流总是偏向于阻抗最低的路径,走最短的路线,即紧挨着高速信号传输线的传输平面,一般情况下为GND地平面。所以一般来说,在打via过孔时,要注意避免过孔把地平面打断,形成ground plane disruption槽,造成高速电路的信号回来路径面积增大,增加噪声辐射,造成EMI超标问题。Ground Plane

设计要求中有提到此网络有2A电流,目前一层铜皮由于过孔隔断无法满足载流要求,需要补强。这样的影响,首先是无法满足载流要求;其次,电流的回流路径加长,增加了噪声。减少PCB上高速信号的噪声辐射的一个基本原则是尽量减少电流回流路径的环路面积,高速信号的回流电流总是偏向于阻抗最低的路径,走最短的路线,即紧挨着高速信号传输线的传输平面,一般情况下为GND地平面。所以一般来说,在打via过孔时,要注意避免过孔把地平面打断,形成ground plane disruption槽,造成高速电路的信号回来路径面积增大,增加噪声辐射,造成EMI超标问题。Ground Plane

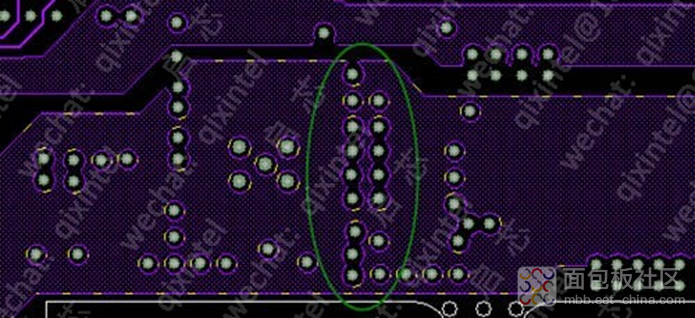

因此,强烈建议打via过孔时,特别是并行数据总线的一排过孔,要注意避免过孔将GND地平面打断,在GDN地平面上形成Slot,阻碍回流路径通道。打过孔是要错开打开或者适当拉开过孔的间距,让过孔之间的GND地平面有铜皮通道让高速信号的回流返回。尤其是,过孔比较多的时候,可以交错打过孔,如上图。这样不仅可以让过孔保持较大的距离,同时,也可以让回流路径尽量短,保证信号质量最优。作者:启芯硬件来源:面包板社区https://mbb.eet-china.com/blog/443713-440345.html

因此,强烈建议打via过孔时,特别是并行数据总线的一排过孔,要注意避免过孔将GND地平面打断,在GDN地平面上形成Slot,阻碍回流路径通道。打过孔是要错开打开或者适当拉开过孔的间距,让过孔之间的GND地平面有铜皮通道让高速信号的回流返回。尤其是,过孔比较多的时候,可以交错打过孔,如上图。这样不仅可以让过孔保持较大的距离,同时,也可以让回流路径尽量短,保证信号质量最优。作者:启芯硬件来源:面包板社区https://mbb.eet-china.com/blog/443713-440345.html

上面这张图,电源被过孔隔断,有瓶颈。需要加强。

上面这张图,电源被过孔隔断,有瓶颈。需要加强。 上图的联排过孔,隔开了电源平面。电源铺铜有瓶颈,需要补强

上图的联排过孔,隔开了电源平面。电源铺铜有瓶颈,需要补强 设计要求中有提到此网络有2A电流,目前一层铜皮由于过孔隔断无法满足载流要求,需要补强。这样的影响,首先是无法满足载流要求;其次,电流的回流路径加长,增加了噪声。减少PCB上高速信号的噪声辐射的一个基本原则是尽量减少电流回流路径的环路面积,高速信号的回流电流总是偏向于阻抗最低的路径,走最短的路线,即紧挨着高速信号传输线的传输平面,一般情况下为GND地平面。所以一般来说,在打via过孔时,要注意避免过孔把地平面打断,形成ground plane disruption槽,造成高速电路的信号回来路径面积增大,增加噪声辐射,造成EMI超标问题。Ground Plane

设计要求中有提到此网络有2A电流,目前一层铜皮由于过孔隔断无法满足载流要求,需要补强。这样的影响,首先是无法满足载流要求;其次,电流的回流路径加长,增加了噪声。减少PCB上高速信号的噪声辐射的一个基本原则是尽量减少电流回流路径的环路面积,高速信号的回流电流总是偏向于阻抗最低的路径,走最短的路线,即紧挨着高速信号传输线的传输平面,一般情况下为GND地平面。所以一般来说,在打via过孔时,要注意避免过孔把地平面打断,形成ground plane disruption槽,造成高速电路的信号回来路径面积增大,增加噪声辐射,造成EMI超标问题。Ground Plane

本篇文章来源于微信公众号: 电子工程专辑

上一篇:

用AD读取编码开关设置的考虑

下一篇:

0Ω电阻,请不要小瞧它